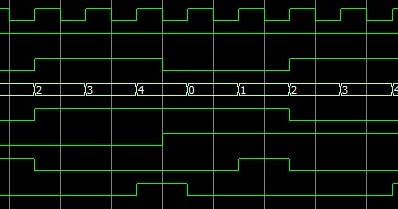

This document will detail the C and VHDL code contained in the LED test reference Design. TN1130 vhdl code for frequency divider crc verilog code 16 bit vhdl code for Clock divider for FPGA 304M TN1141 TN1130 2679SĪbstract: handspring led datasheets ADS7870 XAPP147 XCR3256XL There will also be some overhead time for, of the FPGA (see Table 16-8). The divider value can be set using a parameter, density of the device and the frequency of SEDCLKIN. The default is 1, so the default SEDCLKIN frequency is 2.5 MHz. The divider for SEDCLKIN can be set to 1, 2, 4, 8, 16 or 32. The software default for, range of 2.5 MHz to 66 MHz. MCCLK goes through another divider to create SEDCLKIN. XAPP378 XAPP352: digital clock vhdl code COOLRUNNER-II examples digital clock verilog code COOLRUNNER-II ucf file vhdl code for frequency divider vhdl code for clock divider XAPP378 xilinx vhdl code for digital clock verilog code divide vhdl code for digital clockĪbstract: crc verilog code 16 bit vhdl code for Clock divider for FPGA 304M TN1141 TN1130 2679S All CoolRunner-II VHDL and Verilog attribute examples For more information on entering constraints with the, maintain a separate file for the design constraints.

HDL code examples are available for, without needing to re-synthesize the source code. Both VHDL and Verilog code with test benches are available, , CoolCLOCK, DataGATE, Schmitt trigger inputs, and I/O termination types. The VHDL component declaration syntax for using a clock, Example source code is available for download. Text: and interface of the clock divider unit. Vhdl code for frequency divider Datasheets Context Search Catalog DatasheetĪbstract: COOLRUNNER-II examples digital clock verilog code COOLRUNNER-II ucf file vhdl code for frequency divider vhdl code for clock divider XAPP378 xilinx vhdl code for digital clock verilog code divide vhdl code for digital clock

0 kommentar(er)

0 kommentar(er)